Technical Data Sheet TDS105

# Copper Damascene Fill Plating Using the Solstice CopperMax Reactor

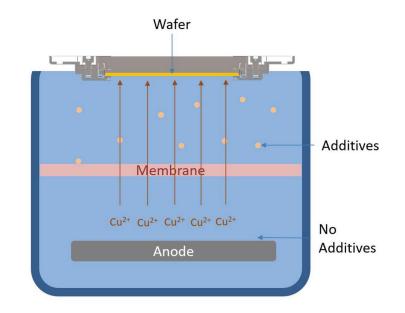

Modern semiconductor copper plating chemistries include expensive, highly-engineered organic additives that serve to enhance the quality of the plating. However, these additives are readily destroyed when they come in contact with the copper anode of the plating system. This necessitates ongoing replenishment of additives and significantly increases process costs.

However, the proprietary Solstice® CopperMax™ reactor integrates a cationic exchange membrane that separates organic additives from the anode while still allowing high-speed copper cation movement to the wafer. This enables higher plating rates while routinely reducing the user's chemistry costs by more than 95% – and also delivering world-class plated feature uniformity.

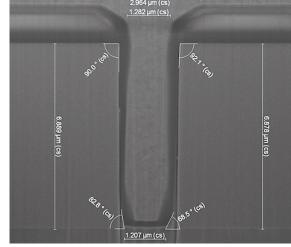

Copper damascene fill plated by the Solstice CopperMax reactor

## **Example Applications**

- Interconnect

- Logic and memory applications

- CMOS backplane wafer

- And more...

#### **Features**

- Cation exchange membrane to reduce additive use

- Continuously filtered chemistry, optional carbon filtration

- High-precision wafer rotation

- Adjustable diffuser

- Dry-contact low-maintenance plating rotor

- Customized seal reach

- Levitronix pump with LeviFlow™

#### **Benefits**

- Additive costs reduced >95%

- Maximized bath life

- Extremely uniform field profile

- Seal reach aligns to existing integration

- Continuously cleaner chemistry

- Precise, consistent flow rate control

#### Eliminating additive breakdown

The proprietary design of the Solstice®

CopperMax™ reactor dramatically reduces

the deterioration of organic additives by

using a cationic exchange membrane to

keep additives from contacting the anode.

This significantly reduces chemistry costs

while enhancing copper plating quality.

In other reactors, the plating behavior shifts rapidly as additives break down. The bath metrology begins to return inaccurate readings, which leads to erroneous dosing.

### **Technical Data**

| ■ Wafer Sizes             | 75-200 mm                  | Configurable to non-standard sizes, e.g., 160 mm |  |

|---------------------------|----------------------------|--------------------------------------------------|--|

| ■ Wafer Thickness         | 150µm to >6mm              |                                                  |  |

| ■ Wafer Materials         | Silicon                    |                                                  |  |

|                           | GaAs                       |                                                  |  |

|                           | GaN on Si, GaN on Sapphire |                                                  |  |

|                           | Sapphire                   |                                                  |  |

|                           | Transparent substrates     | s and more                                       |  |

| Flow Rate                 | 25 lpm                     |                                                  |  |

| Process Time              | <3 min/wafer               | Dependent on feature                             |  |

| ■ Within-Wafer Uniformity | <5% 3-sigma                |                                                  |  |

| Wafer-to-Wafer Uniformity | <1% (mean-to-mean)         |                                                  |  |

| Fill Quality              | Void-free                  |                                                  |  |

| Bath Life                 | 50 amp-hours per liter     | With proper chemistry management                 |  |

|                           |                            |                                                  |  |

TDS105 - 12/20 @ClassOne Technology 2020